EN71NS128C0 Base MCP Stacked Multi-Chip Product (MCP) Flash Memory and RAM 128 Megabit (8M x 16-bit) CMOS 1.8 Volt-only Simultaneous Operation Burst Mode Flash Memory and 64 Megabit (4M x 16-bit) Pseudo Static RAM

## Distinctive Characteristics MCP Features

- Power supply voltage of 1.7V to 1.95V

- High performance

- 70 ns @ random access

- 7 ns @ burst access (108MHz)

Package

- 6.2 x 7.7 x 1.0mm 56 ball BGA

### **General Description**

The EN71NS series is a product line of stacked Multi-Chip Product (MCP) packages and consists of:

- E29NS128 (Burst mode) Flash memory die.

- Pseudo SRAM.

For detailed specifications, Please refer to the individual datasheets listed in the following table.

| Device      | Document  |

|-------------|-----------|

| NOR Flash   | EN29NS128 |

| Pseudo SRAM | ENPSMC5   |

### **Product Selector Guide**

#### **128 Mb Flash Memories**

| Device-Model#                     | EN71NS128C0        | pSRAM density                     | 64M pSRAM                                |  |  |

|-----------------------------------|--------------------|-----------------------------------|------------------------------------------|--|--|

| Flash Access time                 | I ns at Burst Read | pSRAM Access time                 | 70ns at Async. Mode<br>7ns at Burst Read |  |  |

| pSRAM Burst mode<br>max frequency | 108MHz             | pSRAM Burst mode<br>max frequency | 108MHz                                   |  |  |

| Package                           | 56-ball BGA        |                                   |                                          |  |  |

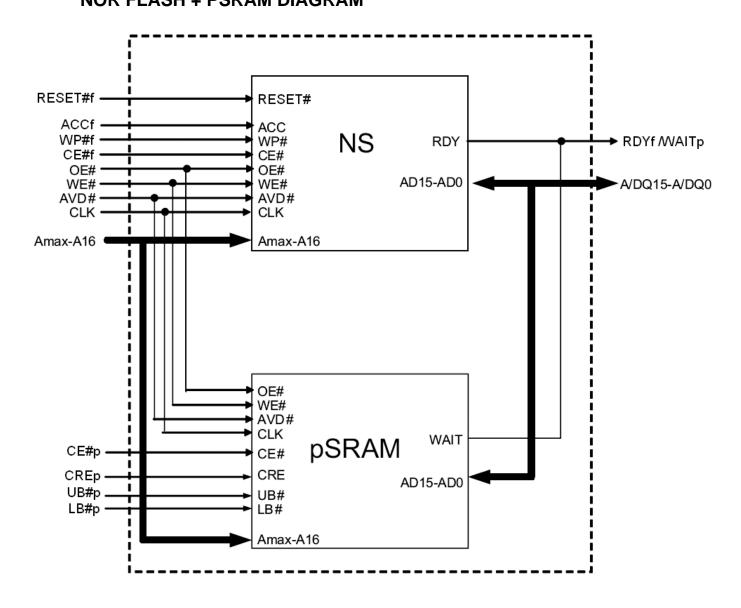

## MCP Block Diagram NOR FLASH + PSRAM DIAGRAM

Note: Amax = A22

### **Connection Diagram**

| МСР         | Flash-only Addresses | Shared Addresses | Shared ADQ Pins |

|-------------|----------------------|------------------|-----------------|

| EN71NS128C0 | A22                  | A21 – A16        | ADQ15 – ADQ0    |

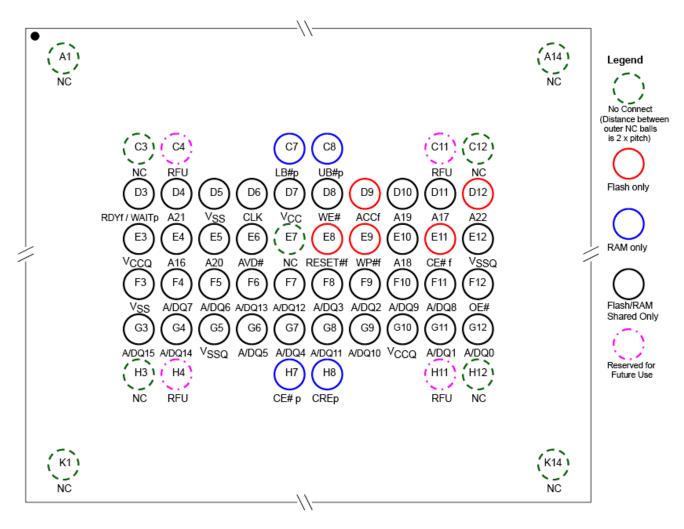

# **Pin Description**

| Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Flash | pSRAM |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

| A22–A16    | Address Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •     | •     |

| ADQ15–ADQ0 | Multiplexed Address/Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •     | •     |

| OE#        | Output Enable input. Asynchronous relative to CLK for the Burst mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ٠     | •     |

| WE#        | Write Enable input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •     | •     |

| VSSQ/VSS   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •     | •     |

| VCCQ/VCC   | Device Power Supply (1.7 V–1.95 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •     | •     |

| NC         | Not Contact; pin not connected internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •     | •     |

| RDYf/WAITp | Ready output; indicates the status of the Burst read.<br>Flash Memory RDY (using default "Active HIGH"<br>configuration)<br>$V_{OL}$ = data invalid,<br>$V_{OH}$ = data valid.<br>Note: The default polarity for the pSRAM WAIT signal is<br>opposite the default polarity of the Flash RDY signal.<br>pSRAM WAIT (using default "Active HIGH" configuration)<br>$V_{OL}$ = data valid,<br>$V_{OH}$ = data invalid.<br>To match polarities, change bit 10 of the pSRAM Bus<br>Configuration Register to 0 (Active LOW WAIT). Alternately,<br>change bit 10 of the Flash Configuration Register to 0 (Active<br>LOW RDY) | •     | •     |

| CLK        | Clock input. In burst mode, after the initial word is output, subsequent active edges of CLK increment the internal address counter. Should be at $V_{OL}$ or $V_{IH}$ while in asynchronous mode.                                                                                                                                                                                                                                                                                                                                                                                                                      | •     | •     |

| AVD#       | Address Valid input. Indicates to device that the valid address<br>is present on the address inputs.<br>$V_{IL}$ = for asynchronous mode, indicates valid address; for<br>burst mode, causes starting address to be latched on rising<br>edge of CLK.<br>$V_{IH}$ = device ignores address inputs                                                                                                                                                                                                                                                                                                                       | •     | •     |

| RESET# f   | Hardware reset input. $V_{IL}$ = device resets and returns to reading array data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •     |       |

| WP#f       | Hardware write protect input. $V_{IL}$ = disables program and<br>erase functions in the four outermost sectors. Should be at $V_{IH}$<br>for all other conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •     |       |

| ACCf       | Accelerated input. At $V_{HH}$ , accelerates programming;<br>automatically places device in Accelerated Program mode. At<br>$V_{IL}$ , disables all program and erase functions. Should be at $V_{IH}$<br>for all other conditions. (Applying high voltage on MCP<br>package is prohibited; otherwise, internal RAM may be<br>damaged easily!)                                                                                                                                                                                                                                                                          | •     |       |

| CE# p      | Chip Enable Input for pSRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | •     |

| CE# f      | Chip Enable Input for Flash. Asynchronous relative to CLK for the Burst mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •     |       |

| CREp       | Control register enable (pSRAM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | •     |

| LB#p       | Lower byte enable. DQ7~DQ0 (pSRAM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | •     |

| UB#p       | Upper byte enable. DQ15~DQ8 (pSRAM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | •     |

| RFU        | Reserved for Future Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |       |

# Operating Mode (For Asynchronous mode)

| Asynchronous Mode<br>BCR[15]=1  | Power   | CLK    | ADV# | CE# | OE# | WE# | CRE | UB#/<br>LB# | WAIT2  | A/DQ[15:0]         |

|---------------------------------|---------|--------|------|-----|-----|-----|-----|-------------|--------|--------------------|

| Read                            | Active  | х      | J    | L   | L   | Н   | L   | L           | Low-z  | Data out           |

| Write                           | Active  | х      | J    | L   | х   | L   | L   | L           | High-z | Data in            |

| Standby                         | Standby | H or L | х    | Н   | х   | х   | L   | х           | High-z | High-z             |

| No operation                    | ldle    | х      | х    | L   | х   | х   | L   | х           | Low-z  | х                  |

| Configuration register<br>write | Active  | х      | J    | L   | Н   | L   | Н   | х           | Low-z  | High-z             |

| Configuration register read     | Active  | х      | J    | L   | L   | Н   | Н   | L           | Low-z  | Config.<br>Reg.out |

#### **Operating Mode (For Synchronous Burst mode)**

| Burst Mode<br>BCR[15]=0         | Power   | CLK    | ADV# | CE# | OE# | WE# | CRE | UB#/<br>LB# | WAIT   | A/DQ[15:0]                |

|---------------------------------|---------|--------|------|-----|-----|-----|-----|-------------|--------|---------------------------|

| Async read                      | Active  | H or L | പ    | L   | L   | н   | L   | L           | Low-z  | Data out                  |

| Async write                     | Active  | H or L | J.   | L   | х   | L   | L   | L           | High-z | Data in                   |

| Standby                         | Standby | H or L | х    | Н   | х   | х   | L   | х           | High-z | High-z                    |

| No operation                    | ldle    | H or L | х    | L   | х   | х   | L   | х           | Low-z  | х                         |

| Initial burst read              | Active  | л      | L    | L   | х   | н   | L   | L           | Low-z  | Address                   |

| Initial burst write             | Active  | л      | L    | L   | Н   | L   | L   | х           | Low-z  | Address                   |

| Burst continue                  | Active  | 57     | Н    | L   | х   | х   | х   | L           | Low-z  | Data out<br>or<br>Data in |

| Configuration register<br>write | Active  | л      | L    | L   | Н   | L   | Н   | Х           | Low    | High-z                    |

| Configuration register read     | Active  | л      | L    | L   | L   | Н   | Н   | L           | Low    | Config.<br>Reg.out        |

Note: X=don't care. H=logic high. L=logic low. V= Valid data

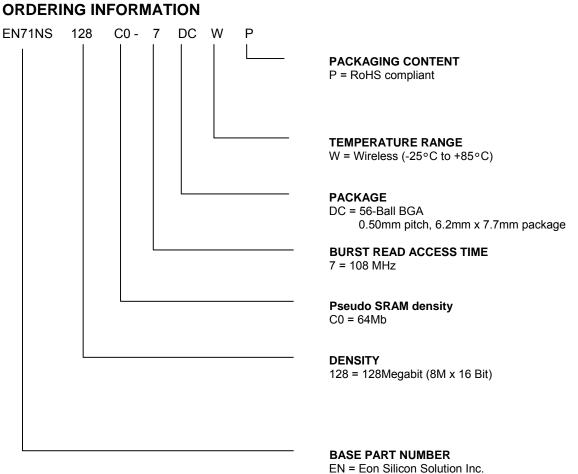

EN = Eon Silicon Solution Inc. 71NS = Multi-chip Product (MCP) 1.8V Simultaneous Read/Write, Burst-mode Multiplexed Flash and RAM

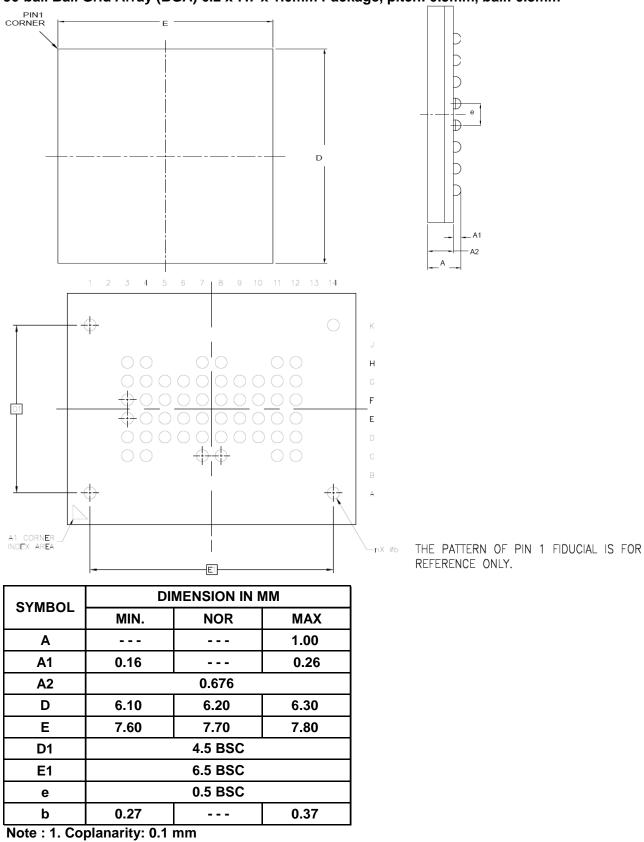

### PACKAGE MECHANICAL

56-ball Ball Grid Array (BGA) 6.2 x 7.7 x 1.0mm Package, pitch: 0.5mm, ball: 0.3mm

This Data Sheet may be revised by subsequent versions 7 ©2004 Eon Silicon Solution, Inc., www.eonssi.com or modifications due to changes in technical specifications.

#### **Revisions List**

| Revision No | Description                                 | Date       |

|-------------|---------------------------------------------|------------|

| А           | Initial Release                             | 2010/11/23 |

| В           | Change Pseudo SRAM from ENPSS64 to ENPSMC5. | 2011/06/16 |